PECL、LVDS和CML电平

发布日期:2019-07-24

点击次数:1492

PECL、LVDS和CML电平

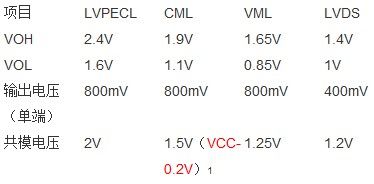

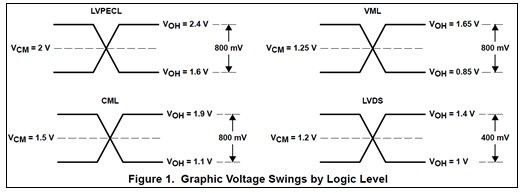

芯片间互连通常有三种接口:PECL(Positive Emitter-Coupled Logic)、LVDS(Low-Voltage Differential Signals)、CML(Current Mode Logic)。

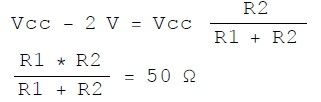

ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。以上三种均为射随输出结构,必须有电阻拉到一个直流偏置电压。(如多用于时钟的LVPECL:直流匹配时用130欧上拉,同时用82欧下拉;交流匹配时用82欧上拉,同时用130欧下拉。但两种方式工作后直流电平都在1.95V左右。)

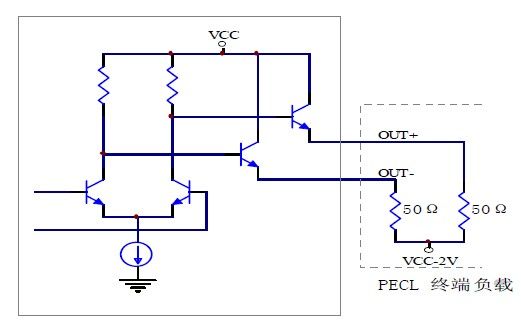

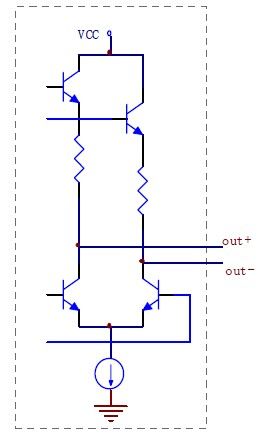

1.1. PECL接口输出结构

PECL 电路的输出结构如图所示,包含一个差分对和一对射随器。输出射随器工作在正电源范围内,其电流始终存在,这样有利于提高开关速度。标准的输出负载是接50Ω至VCC-2V的电平上,如图中所示,在这种负载条件下,OUT+与OUT-的静态电平典型值为VCC-1.3V,OUT+与OUT-输出电流为14mA。PECL 结构的输出阻抗很低,典型值为4~ 5 Ω,这表明它有很强的驱动能力,但当负载与PECL 的输出端之间有一段传输线时,低的阻抗造成的失配将导致信号时域波形的振铃现象。

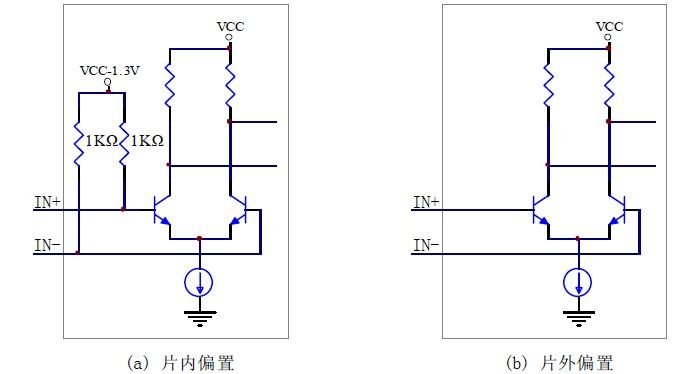

1.2. PECL接口输入结构

PECL 输入结构如图2所示,它是一个具有高输入阻抗的差分对。该差分对共模输入电压需偏置到VCC-1.3V,这样允许的输入信号电平动态最大。MAXIM 公司的PECL 接口有两种形式的输入结构,一种是在芯片上已加有偏置电路,如MAX3867、MAX3675,另一种则需要外加直流偏置。

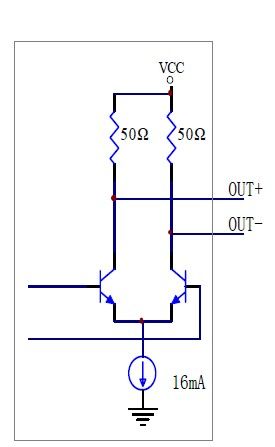

2.1. CML接口输出结构

CML 接口的输出电路形式是一个差分对,该差分对的集电极电阻为50Ω,如图中所示,输出信号的高低电平切换是靠共发射极差分对的开关控制的,差分对的发射极到地的恒流源典型值为16mA,假定CML 输出负载为一50Ω上拉电阻,则单端CML 输出信号的摆幅为Vcc~Vcc-0.4V。在这种情况下,差分输出信号摆幅为800mV,共模电压为Vcc-0.2V。若CML输出采用交流耦合至50Ω负载,这时的直流阻抗有集电极电阻决定,为50Ω,CML 输出共模电压变为Vcc-0.4V,差分信号摆幅仍为800mV。在交流和直流耦合情况下输出波形见图。

CML 输出结构

CML在不同负载时的输出波形

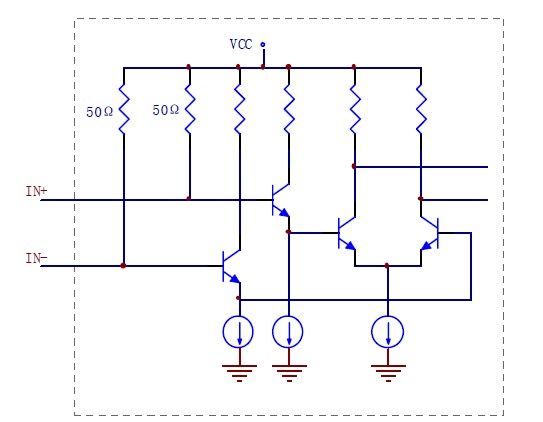

2.2. CML接口输入结构

CML 输入结构有几个重要特点,这也使它在高速数据传输中成为常用的方式,如图5所示,MAXIM 公司的CML 输入阻抗为50Ω,容易使用。输入晶体管作为射随器,后面驱动一差分放大器。

3.1. LVDS接口输出结构

MAXIM 公司LVDS 输出结构在低功耗和速度方面做了优化,电路如图6所示。电路差分输出阻抗为100Ω。

LVDS输出结构

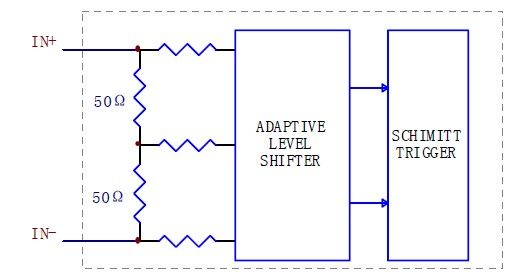

3.2. LVDS接口输入结构

LVDS 输入结构如图所示,输入差分阻抗为100Ω,为适应共模电压宽范围内的变化,输入级还包括一个自动电平调整电路,该电路将共模电压调整为一固定值,该电路后面是一个SCHMITT触发器。SCHMITT 触发器为防止不稳定,设计有一定的回滞特性,SCHIMTT 后级是差分放大器。

LVDS输入结构

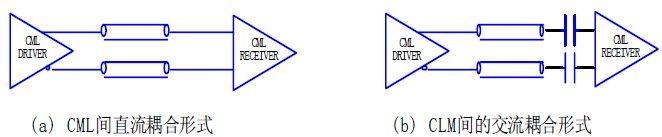

4.1. CML到CML的连接

CML 到CML 之间连接分两种情况,当收发两端的器件使用相同的电源时,CML 到CML 可以采用直流耦合方式,这时不需加任何器件;当收发两端器件采用不同电源时,一般要考虑交流耦合,如图中所示,注意这时选用的耦合电容要足够大,以避免在较长连0 或连1 情况出现时,接收端差分电压变小。

CML到CML之间的连接

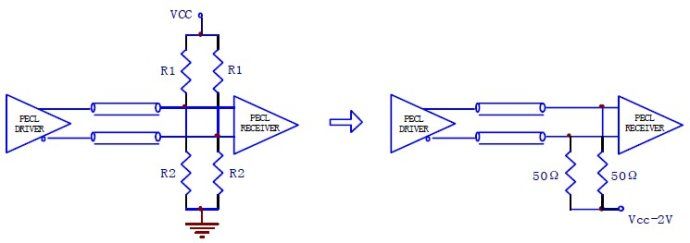

4.2. PECL到PECL的连接

4.2.1. 直流耦合情况

等效电路形式

该等效电路应满足如下方程:

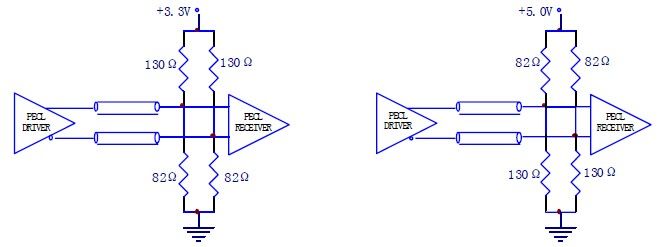

在3.3V 供电时,电阻按5%的精度选取,R1 为130Ω,R2 为82Ω。而在5V 供电时,R1为82Ω,R2 为130Ω。下图给出了这两种供电情况时的详细电路。

PECL电路间直流耦合

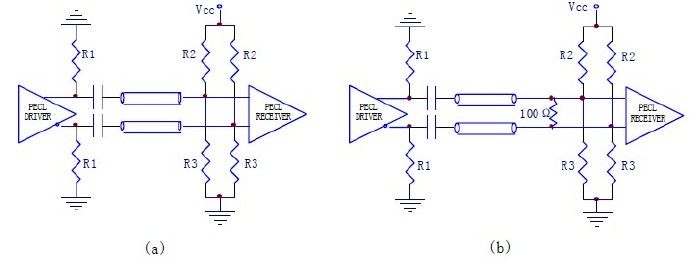

4.2.2. 交流耦合情况

PECL 在交流耦合输出到50Ω的终端负载时,要考虑PECL 的输出端加一直流偏置电阻,如图所示。

PECL电路间交流耦合

PECL 的输出共模电压需固定在Vcc-1.3V,在选择直流偏置电阻时仅需该电阻能够提供14mA 到地的通路,这样R1=(Vcc-1.3V)/14mA。在3.3V 供电时,R1=142Ω,5V 供电时,R1=270Ω。然而这种方式给出的交流负载阻抗低于50Ω,在实际应用中,3.3V 供电时,R1 可以从142Ω到200Ω之间选取,5V 供电时,R1 可以从270Ω到350Ω之间选取,原则是让输出波形达到最佳。

PECL 交流耦合另外有两种改进结构,一种是在信号通路上串接一个电阻,从而可以增大交流负载阻抗使之接近50Ω;另一种方式是在直流偏置通道上串接电感,以减少该偏置通道影响交流阻抗。

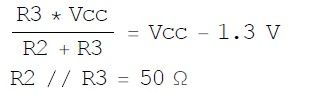

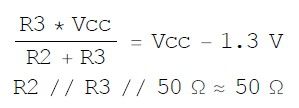

上图中R1和R2 的选择应考虑如下几点:(1)PECL 输入直流偏压应固定在Vcc-1.3V;(2)输入阻抗应等于传输线阻抗;(3)低功耗;(4)外围器件少。最常用的就是图11 中的两种。在上图(a)中,R1 和R2 的选择应满足下面方程组:

求解得到:

R2 = 82 Ω and R3 = 130 Ω +3.3 V供电时

R2 = 68 Ω and R3 = 180 Ω +5 V供电时

图(a)有一个缺点就是它的功耗较大,当对功耗有要求时,可以采用图(b)所示的结构,在这种情况下,R2 和R3 需满足如下方程组:

R2 和R3 通常选:

R2 = 2.7 KΩ and R3 = 4.3 KΩ +3.3 V供电时

R2 = 2.7 KΩ and R3 = 7.8 KΩ +5 V供电时

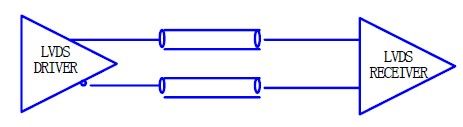

4.3. LVDS到LVDS的连接

因为LVDS 的输入与输出都是内匹配的,所以LVDS 间的连接可以如图中那样直接连接。

LVDS间连接

深圳市晶友嘉电子有限公司在频率器件行业已发展超过14年, 具备国际标准体系ISO9001、ISO14001等认证, 在深圳建有生产基地,能快速化响应市场需求,供应性能稳定和高性价比的贴片和插件晶振;

贴片晶振产品广泛的应用在电源管理、仪器仪表、PC及周边小家电、通讯产品、逻辑电路、应用于DVB (数字机顶盒)、GPS(卫星定位)、DVD及数码相框、高性能MODEM、路由器、VPN接入服务器、无线路由器、网络存储设备(NAS)、VOIP网关、数字硬盘录像机(Digital video recorder, DVR)、DSLAMs、高端打印机、教学演示网络设备、交换机、机顶盒、税控机、液晶显示驱动、鼠标、键盘、蓝牙音响、车载MP3、LCD控制板。

应用领域:新能源汽车电子、智能机器人、无人机、医疗电子、2.4G无线通讯、微波通信、光网络通讯、蓝牙、移动终端、物联网、工业控制、及安防行业都取得一定的市场占有率。

晶友嘉提供专业贴片晶振、有源晶振、差分晶振、声表谐振器等产品生产和供应,满足您的所有晶振产品需求,电话:0755-32840201,欢迎来厂莅临指导。

贴片晶振产品广泛的应用在电源管理、仪器仪表、PC及周边小家电、通讯产品、逻辑电路、应用于DVB (数字机顶盒)、GPS(卫星定位)、DVD及数码相框、高性能MODEM、路由器、VPN接入服务器、无线路由器、网络存储设备(NAS)、VOIP网关、数字硬盘录像机(Digital video recorder, DVR)、DSLAMs、高端打印机、教学演示网络设备、交换机、机顶盒、税控机、液晶显示驱动、鼠标、键盘、蓝牙音响、车载MP3、LCD控制板。

应用领域:新能源汽车电子、智能机器人、无人机、医疗电子、2.4G无线通讯、微波通信、光网络通讯、蓝牙、移动终端、物联网、工业控制、及安防行业都取得一定的市场占有率。

晶友嘉提供专业贴片晶振、有源晶振、差分晶振、声表谐振器等产品生产和供应,满足您的所有晶振产品需求,电话:0755-32840201,欢迎来厂莅临指导。